How to enable PCIe Endpoint Mode?(CM5 ubuntu 22.05)

-

Cannot set the system to PCIe EndPoint mode, how? the RK3588 support PCIe EndPoint Mode.

-

@blank The PCIE ep mode requires modifications to the software and hardware, and the software dts configuration is sufficient. The hardware modification RC clock is directly connected to RK3568. The current board hardware configuration can only work in RC mode.

diff --git a/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb-v11.dts b/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb-v11.dts index 5b04c9d3f354..4da6083e288a 100755 --- a/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb-v11.dts +++ b/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb-v11.dts @@ -1305,6 +1305,7 @@ &pcie3x4 { //express &pcie3x2 { + compatible = "rockchip,rk3588-pcie-ep", "snps,dw-pcie"; reset-gpios = <&gpio3 RK_PB0 GPIO_ACTIVE_HIGH>; vpcie3v3-supply = <&vcc3v3_sys>; status = "okay"; -

@george Can we disable the RC clock (by remove the Clock-Chip on PCB) and turn it into EP mode? I guess this will disable the PCIe-Eth too, but I can accept that. Thanks.

-

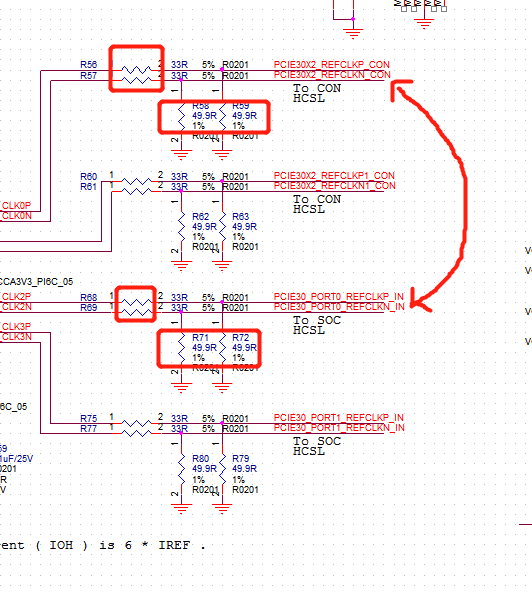

@blank Sorry, there was an issue with the reply yesterday. Currently, only the M2 interface has EP functionality. The hardware operation is shown in the following figure (the clock directly skips the PLL chip), and the software can be modified as follows.

diff --git a/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb-v11.dts b/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb-v11.dts index 5b04c9d3f354..3c4ff40742e7 100755 --- a/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb-v11.dts +++ b/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb-v11.dts @@ -1297,6 +1297,7 @@ &sata1 { //ssd &pcie3x4 { + compatible = "rockchip,rk3588-pcie-ep", "snps,dw-pcie"; num-lanes = <2>; reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>; vpcie3v3-supply = <&vcc3v3_sys>; -

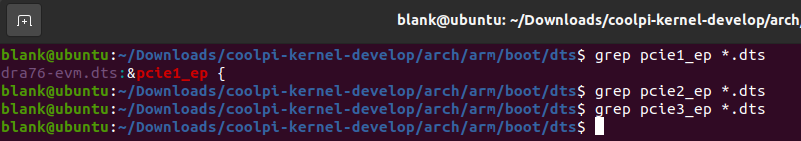

@george Looks like only PCIe1 can be set to EP mode, the SSD PCIe3 cant.

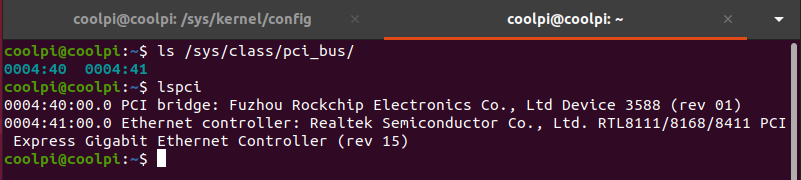

And I tried your method, still can't find "/sys/class/pci_ep" device, we have to switch to Nvidia Platform....; Or, do you have other ideas? Thanks. -

@blank Official document description: The pcie30x4 controller operates in EP mode and can be used in 4Lane mode or 2Lane mode using pcie30phy's port0. The 2lane in pcie30phy's port1 can be used as an RC in conjunction with other controllers.

- The SSD of the CM5 machine corresponds to the PCIE30 PORT0 interface